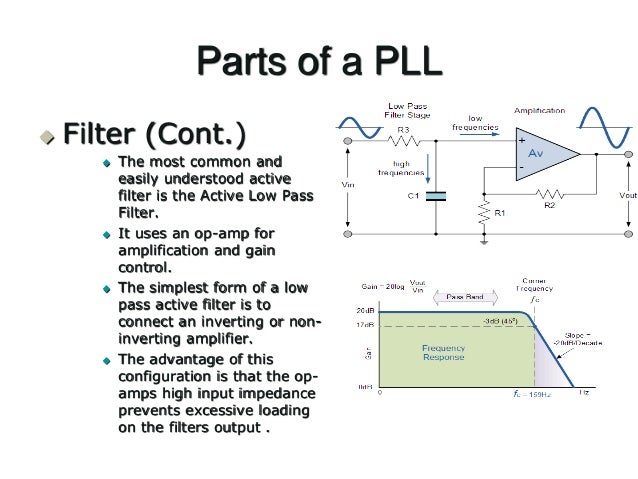

A survival guide to scaling your PLL loop filter design - Analog - Technical articles - TI E2E support forums

A survival guide to scaling your PLL loop filter design - Analog - Technical articles - TI E2E support forums

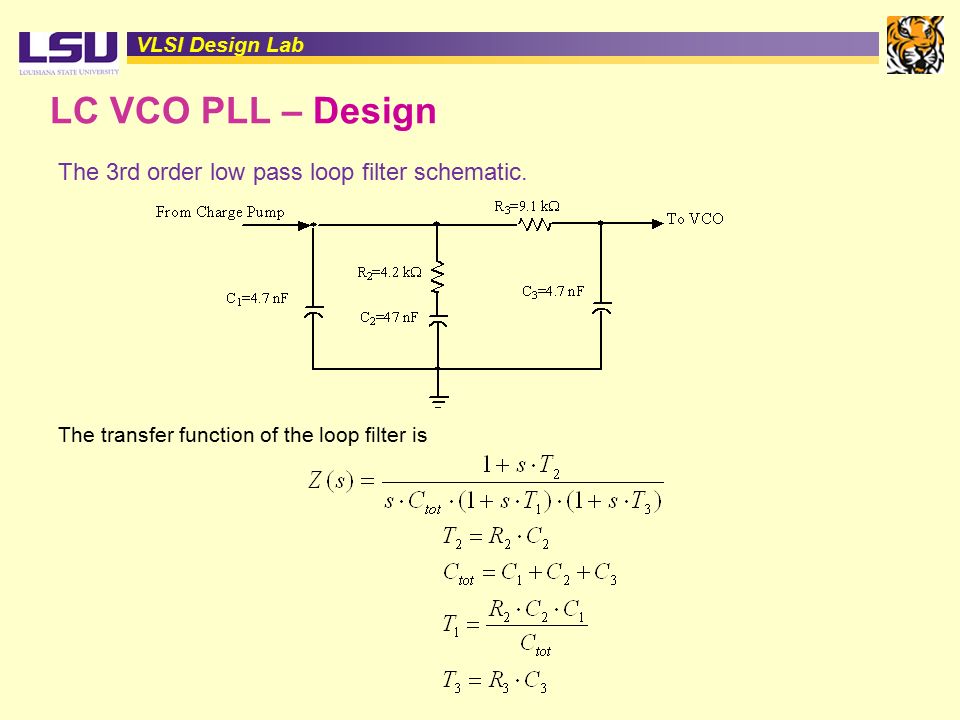

Sensors | Free Full-Text | Analysis and Design of Integrated Blocks for a 6.25 GHz Spacefibre PLL | HTML